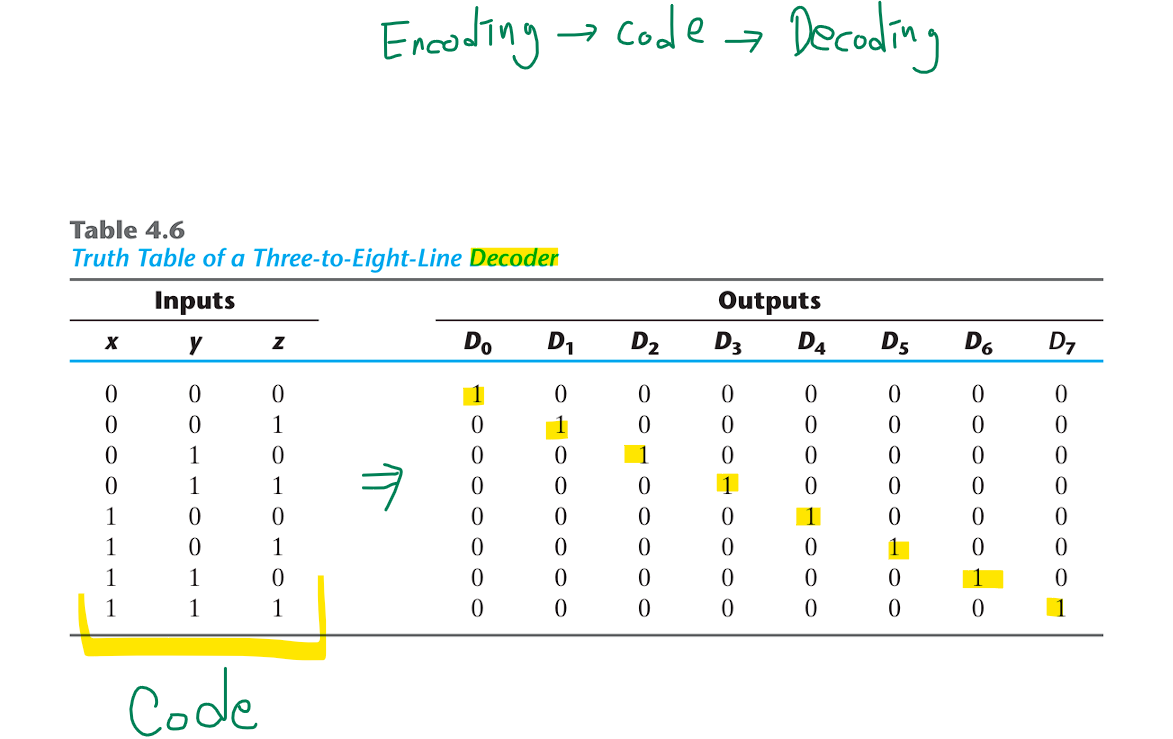

Decoders

- 3-to-8 Decoder

우리는 Code로 암호화하는 encoding 작업이 필요하다 그 이유는 컴퓨터가 이해할 수 있게 만들기 위해서다 이러한 code들을 Decoder를 통해서 우리가 이해할 수 있게 하는 작업도 필요하다.

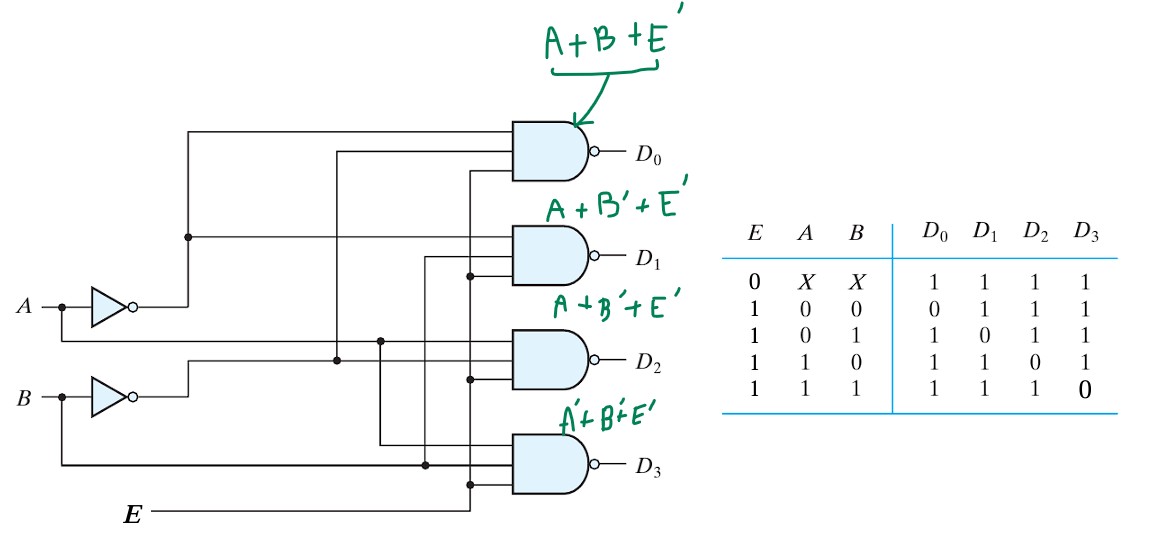

이러한 Decoder를 설계하면 위 그림처럼 나타낼 수 있다. 하지만 AND의 크기가 NAND or NOR 보다 커서 특히 NAND의 크기가 매우 작아 선호도가 높아 NAND로 변환하게 되면

위 그림과 같이 생성되게 된다. Enable을 연결해줘서 동작 기능을 형성할 수 있다. Enable이 "0" 일 때에는 D0~D3까지 "1"이 나오게 된다. Enable이 "1"일 때가 되서야 D0부터~D3까지 "0"으로 동작이 되어진다 여기서 "0"으로 동작이 되어지는 이유는 NAND gate를 사용하기 위해서 "low enable"을 사용했다. low enable은 '0'일때 동작한다.

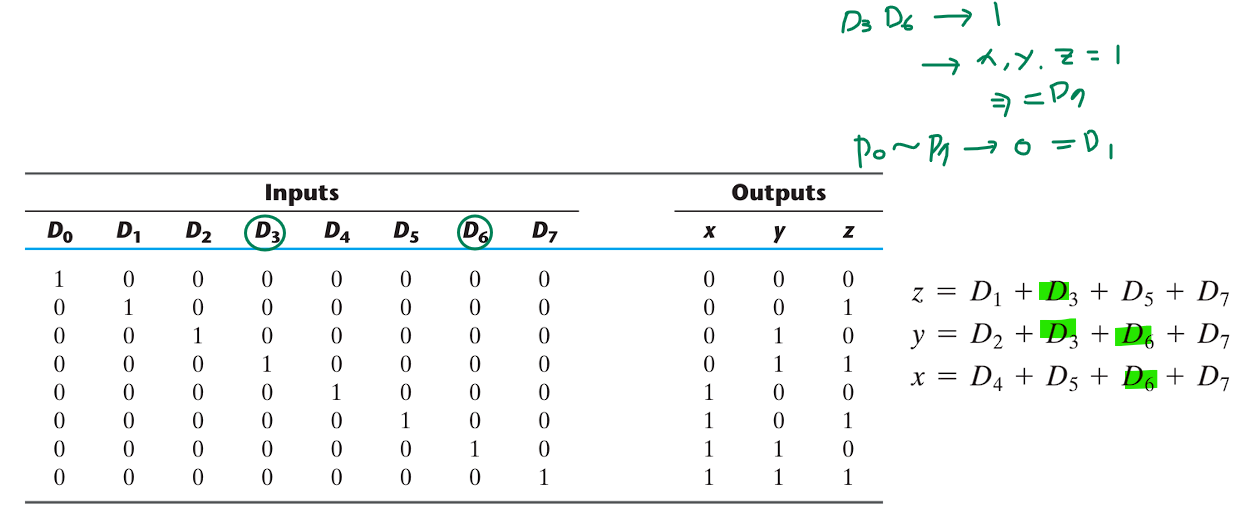

Eecoder

이번에는 Encoder의 경우에서 살펴봐야하는데 여기서 문제는 D3와 D6 동시에 1인 경우에는 x,y,z=1 모두 1 이 나와서 D7과 같은 값이 되고 혹은 모두 0일 경우 D1과 동일한 경우로 형성이 된다. 이 경우를 따져야한다.

이러한 두 가지 경우를 고려해서 새롭게 형성하면, V=D0+D1+D2+D3 로 만들어 질 수 있고 모두가 "0"이여야만 "0"으로 x와 y의 유무와 관계없이 멈출 수 있다. 그 외에 하나라도 '1'이 형성이 되면 x와 y의 값에 변하는데 여기서 우선 순위가 존재한다. 즉, D0<D1<D2<D3 로 D3가 '1'이면 D0,1,2 의 값과 관련없어진다.

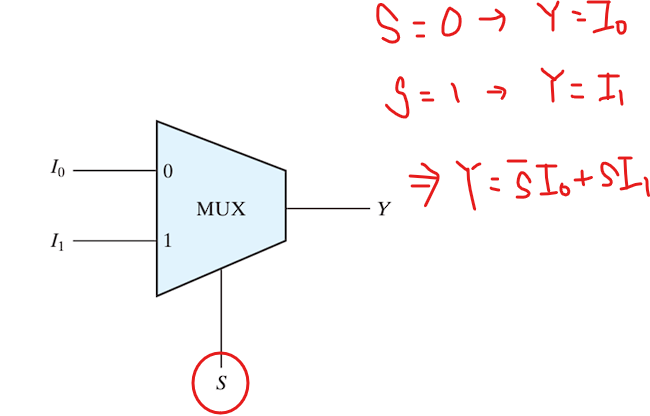

Multiplexer