Revisit Structure of MOSFETs

우선 nMOS와 pMOS의 특징부터 살펴보고 갈려고 한다. nMOS의 경우에는 Gate에 +전하를 인가해주면 - chennal이 형성이 되고 elctorn이 source to drain으로 흘러가게 된다. 즉 "1"일때 ON이라고 얘기 할 수 있다. 또는 high gate voltgae일때 "ON"이라고 할 수 있다.

pMOS의 경우에는 Gate에 0V이하의 전하를 걸어주게 되면 +chennal이 형성이 되고, Souce to Drain으로 +의 전하가 흘러가게 된다. 이를 Hole들의 이동이라고 하고 low gate voltage일때 turn on이 된다고 할 수 있다. 즉 "0"일때 ON인 not gate라고 할 수 있다.

pMOS에 대해서 좀 더 살펴보자면 Gate에는 낮은 voltage를 인가하게 되고 Vgs <0 작아야만 한다. 그리고 또한 Vgs< Vth 작아야 turn on이 된다. pMOS와 비슷하게 Source의 전압 Vg-Vth 전압 Vd의 전압 순서대로 크기가 결정된다

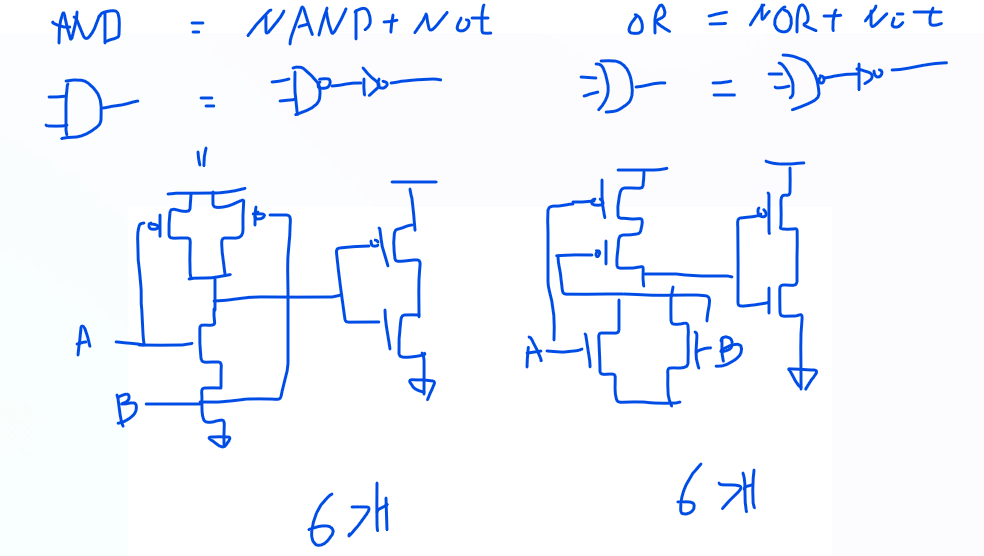

AND2 or OR2 Gate

소제목

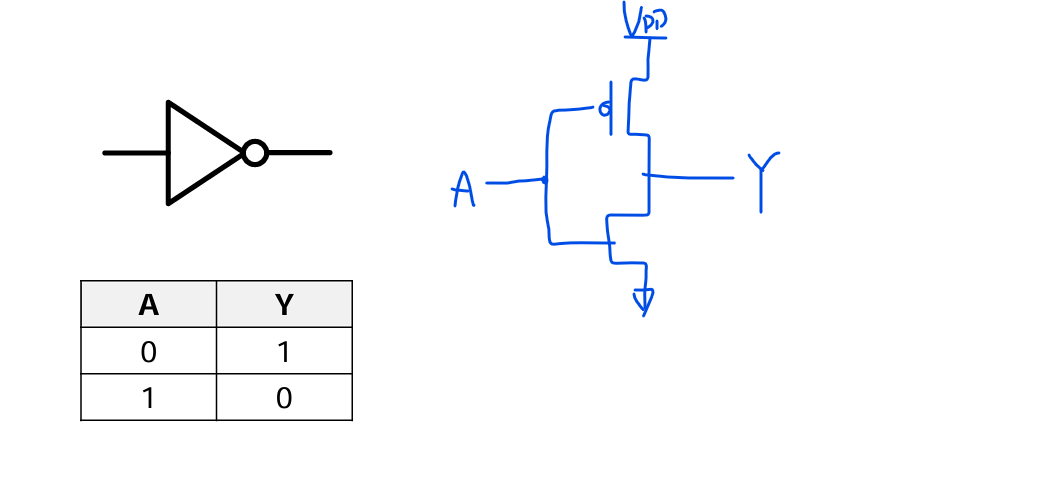

Inverter

Design AND & OR

NAND = F=¯X1+¯X2

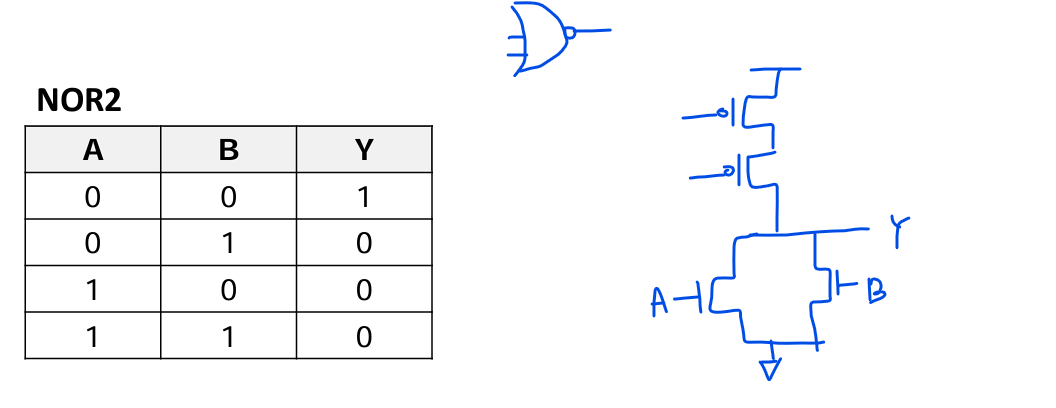

NOR=

F=¯X1∙¯X2

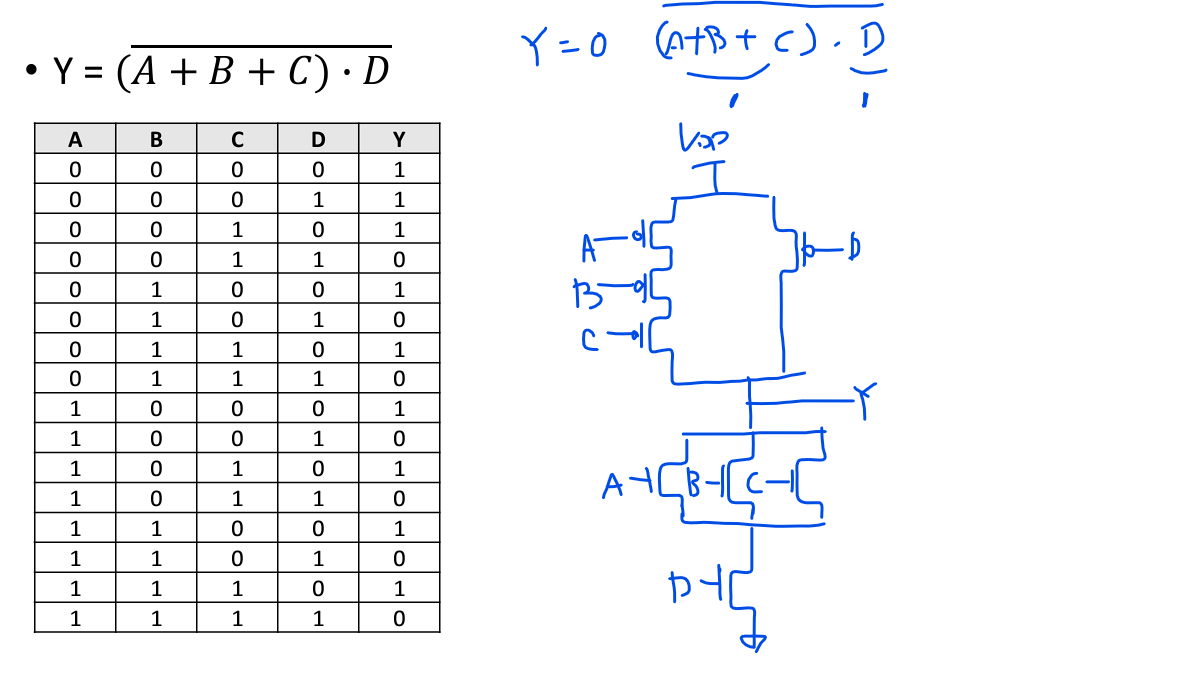

Compound Gate

Y=0 인 시점을 찾아야한다. 먼저 A,B,C 셋중 하나가 1이여야하고 D가 1 이여야한다. 그럼 ABC는 병렬로 D는 직렬로 연결 되어이서 ground와 연결되어지면 되고, Vdd와 연결되는 점은 이와 역으로 ABC가 직렬 D와는 병렬로 연결되면 된다.

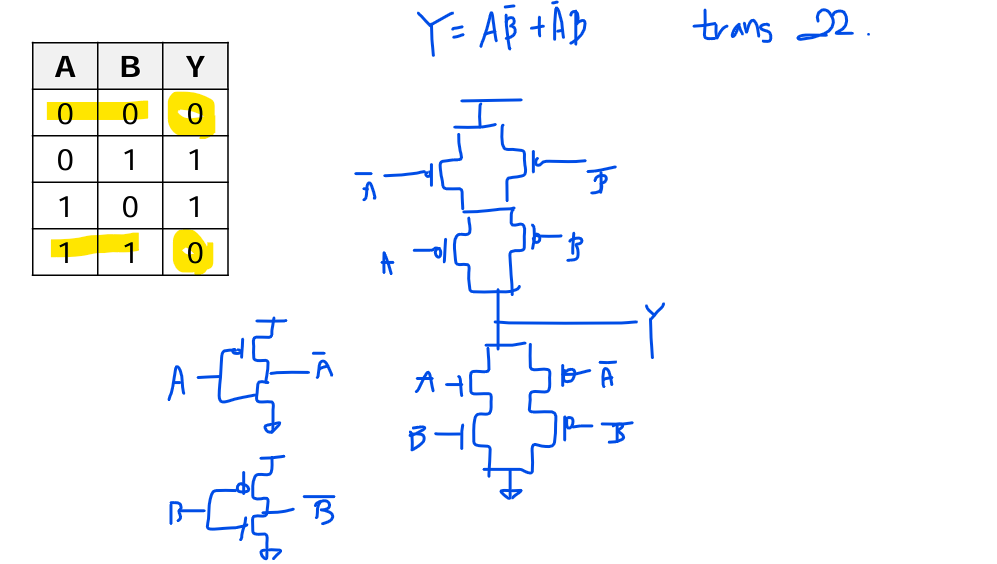

XOR