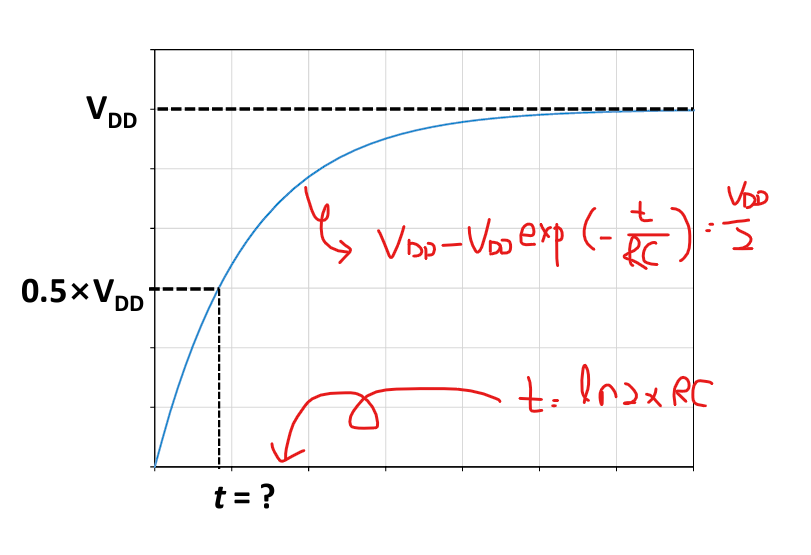

회로에서 input의 변화를 0V -> 3.3v로 준다면,

RC Circuit

RC Delay Model을 통해서 비선형적인 MOSFET의 특징을 대략화 할 수 있다.

$$ \frac{V_{DD}-V_{Y}}{R}=C\frac{\mathrm{d} V_{Y}}{\mathrm{d} t}\\

\frac{\mathrm{d} V_{Y}}{\mathrm{d} t}+\frac{1}{RC}V_{Y}=\frac{V_{DD}}{RC}\\

V_{Y}=V_{DD}+Aexp(kt)\\

kAexp(kt)+\frac{V_{DD}}{RC}+\frac{A}{RC}exp(kt)=\frac{V_{DD}}{RC}\\

k= -\frac{1}{RC} \;\; V_{Y}=V_{DD}(1-exp(\frac{t}{\tau }))$$

Delay in From RC Circuit

Gate Delay를 RC Circuit으로 구하면 t =RC를 통해서 gate Delay에 대해서 접근 할 수 있다.

MOSFET을 conditonally Resistor로 구현

$R\propto \frac{L}{W}$ 저항 R은 L [길이]와는 비례 W[폭]과는 반비례 하는 특성을 이해하고 있다.

여기서 L[길이]sms 가장 작은 크기로 고정되어져 있고 $R\propto \frac{1}{W}$ W의 값에 의해서 R 값이 정해진다.

W=kW일때 저항은 R/k의 값으로 된다.

Gate and Diffusion capacitor

unit-width MOSFET $C_{gate}=C_{drian}=C_{source}=C$

k time of unit width $C_{gate}=C_{drian}=C_{source}={\color{Blue} k}C$

Equivalent RC Circuits; inverter

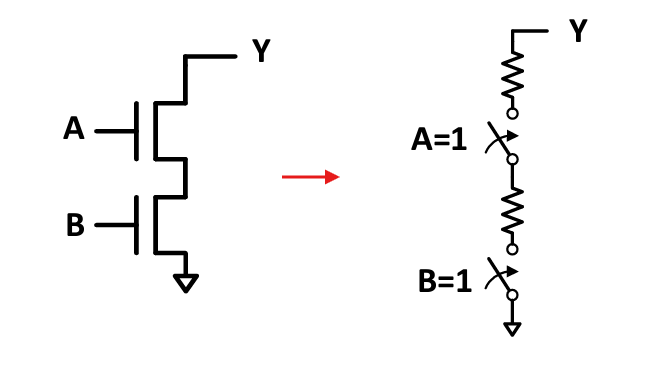

Equivalent RC Circuit NAND2

이번엔 NAND2의 RC model에 대한 Falling을 살펴 볼려고 한다. nMOSFET의 경우를 살펴보면 저항R이 1/3 일려면, With는 6으로 돼어야 한다. 그리고 pMOS의 경우는 3이라고 생각할 수 도 있는데 둘 중 하나만 켜진다는 전제로 가면 6이 맞다

Falling 관점에 대해서 살펴보면 54C로 capacitor가 잡히는데 이 뿐만 아니라 밑에 양 옆 Capacitor 6에 대해서도 생각해주면 12C가 잡혀있어야한다.

First order Approximation

Elmore Delay

Generalization of RC tree delay