Input Impedance in CS vs CG

(Vout 같은 경우는 Rout을 뺀 나머지 전압이 output 전압이기 때문에 output Impedance는 작은 것이 좋고 input impedance는 Rin x I = Vin이고 이것이 GVin으로 vout을 정하기 때문에 input impedance는 큰 것이 좋다)

Cascode에 대해서 살펴 보기전에 CS와 CG의 특징에 대해서 한번 더 되짚어 볼려고 하는데, Common source의 경우 Cgd의 밀러 effect로 인해서 gain이 증가하면 input impedance가 감소하게 된다. low frequency에서는 input impedance가 커서 좋았지만 high frequency에서는 miller's effect로 인해서 input impednace가 작아지는 경우가 생긴다.

Commom gate의 경우 원래 input impedance 1/gm이기 때문에 굉장히 작았지만 캐패시터에 의해 줄어드는 임피던스 또한 작기 때문에 frequency가 높아진다고 input impedance가 깎이는 양이 크지느 않다. 즉, Miller's effect로 부터 자유롭다.

At Low Frequency

이 둘의 이점을 합치기 위해서 cascode를 사용하는 것이 cascode의 주요 목적이다.

만약 Rd <<ro 라면 1번의 figure에서는 gmRd로 ro의 값을 고려하지 않게 되고, 2번의 값에서는

$-g_{m1}r_{o1}\times \frac{\frac{1}{g_{m2}}}{r_{o1}+\frac{1}{gm2}}$ 가 되고 ro1이 1/gm2 보다 굉장히 크기 때문에 결국 $-\frac{g_{m1}}{g_{m2}}$ 로 나오게 된다. $g_{m2}R_{D}$를 곱하게 되면 최종적으로 $ -g_{m1}R_{D}$ 가 나오게 된다.

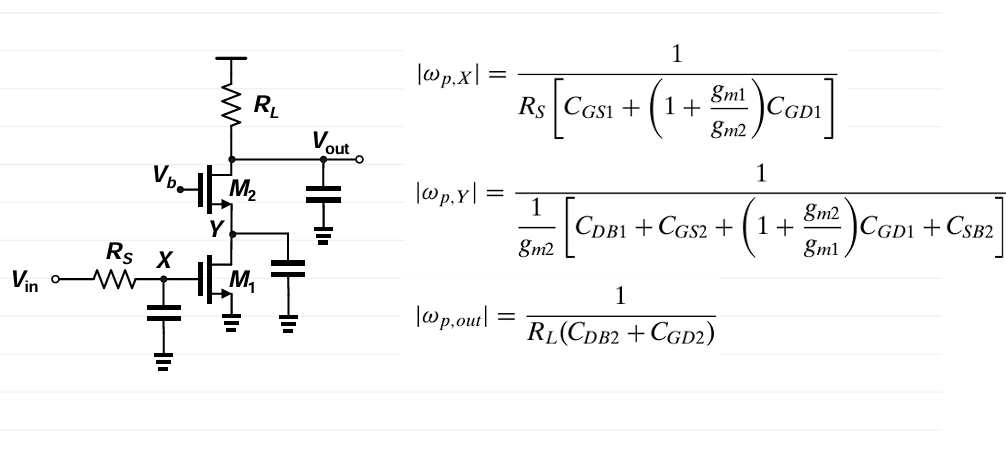

Poles of Cascode Stage

앞서 ro가 굉장히 크다면 gain이 굉장히 작아지는 않좋은 영향에 대해서 살펴보았는데 miller's effect 관점에서는 gain이 작아지면 Zin가 커지기 때문에 impedance 관점에서는 효과적이다. 이를 통해 위에 pole을 구해보면 위의 식 처럼 pole이 구성되어진다.

Example

이 문제에 대해서 풀어보게 되면

이를 기반으로 w(p.out)이 pole을 정한다는 것을 알 수 있고

common soure 의경우 220MHz에서 시작하는 것에 반해 cascode는 440Mhz로 bandwith가 훨 씬 넓다는 것을 알 수 있다.

Capacitances in MOSFET Differentail Pairs

High frequency에서의 변화를 확인 하기 위해서 pole을 구하려고 하는데 Differentail Pari의 경우 half curcuit을 통해서 pole 을 확인 할 수 있다. Iss 부분은 ground 처리를 해주고 구해주면

$$\left| w_{p,X} \right| = \frac{1}{R_{S}\left [ C_{GS1}+(1+\frac{gm1}{gm2})C_{GD1} \right ]}\\\left|w_{p,Y} \right| =\frac{1}{\frac{1}{g3}[C_{DB1}+C_{GS3}+(1+\frac{gm3}{gm1})C_{GD1}+C_{SB3}]}\\\left| w_{p,out} \right|=\frac{1}{R_{L}(C_{DB3}+C_{GD3})}$$

pole 이라는 것은 어느 frequency에서 gain이 깎이는지를 알기 위해서 공부하는 것이다. 그래서 제일 작은 pole을 구하는 것이 목적이다.

'전자공학' 카테고리의 다른 글

| [전자회로] 8장 Op amp (0) | 2024.09.13 |

|---|---|

| [전자회로] 12장 라자비 Feedback system & gain error (1) | 2024.07.22 |

| [전자회로] 라자비 전자회로 Razavi 0장 Amplifier (0) | 2024.07.07 |